Privacy statement: Your privacy is very important to Us. Our company promises not to disclose your personal information to any external company with out your explicit permission.

![]() June 10, 2023

June 10, 2023

1. Basic Concepts of Reflow

In the schematic diagram of a digital circuit, the propagation of digital signals is from one logic gate to another logic gate. The signal is sent from the output end to the receiving end through wires. It seems to flow in one direction. Many digital engineers therefore think that the loop path is Irrelevant, after all, both the driver and receiver are specified as voltage mode devices, so why bother with current! In fact, basic circuit theory tells us that signals are propagated by current, specifically, the movement of electrons, and one of the properties of electron flow is that electrons never stay anywhere, no matter where the current flows, it must come back, so Current always flows in a loop, and any signal in the circuit exists in the form of a closed loop. For high-frequency signal transmission, it is actually a process of charging the dielectric capacitor sandwiched between the transmission line and the DC layer.

2. The effect of backflow

Digital circuits usually rely on ground and power planes to accomplish reflow. The return paths of high-frequency signals and low-frequency signals are different. The low-frequency signal returns the path with the lowest impedance, and the high-frequency signal returns the path with the lowest inductance.

When the current starts from the driver of the signal, flows through the signal line, and is injected into the receiving end of the signal, there is always a return current in the opposite direction: starting from the ground pin of the load, passing through the copper-clad plane, flowing to the signal source, and flowing through The current on the signal wire forms a closed loop. The noise frequency caused by the current flowing through the copper plane is equivalent to the signal frequency. The higher the signal frequency, the higher the noise frequency. The logic gate does not respond to the absolute input signal, but to the difference between the input signal and the reference pin. A single-point terminated circuit reacts to the difference between the incoming signal and its logical ground reference plane, so disturbances in the ground reference plane are as important as disturbances in the signal path. The logic gate responds to an input pin and a designated reference pin, and we don't know which is the designated reference pin (usually negative supply for TTL, positive supply for ECL, but not all), With this property, the anti-jamming capability of differential signals can have a good effect on ground bounce noise and power plane slippage.

When many digital signals on the PCB are switched synchronously (such as CPU data bus, address bus, etc.), this causes transient load current to flow from the power supply into the circuit or from the circuit into the ground wire. Impedance, synchronous switching noise (SSN) will be generated, and ground plane bounce noise (referred to as ground bounce) will also appear on the ground wire. When the surrounding area of the power lines and grounding lines on the printed board is larger, their radiation energy is larger. Therefore, we analyze the switching state of the digital chip, and take measures to control the return flow method to reduce the surrounding area. area, the purpose of the minimum radiation level.

Example explanation:

IC1 is the signal output terminal, IC2 is the signal input terminal (in order to simplify the PCB model, it is assumed that the receiving terminal contains a lower resistor), and the third layer is the ground layer. Both IC1 and IC2 grounds come from the third ground plane. The upper right corner of the TOP layer is a power supply plane, which is connected to the positive pole of the power supply. C1 and C2 are the decoupling capacitors of IC1 and IC2, respectively. The power supply and ground pins of the chip shown in the figure are the power supply and ground of the transmitting and receiving signal terminals.

At low frequency, if the S1 terminal outputs a high level, the entire current loop is that the power supply is connected to the VCC power plane through the wire, and then enters the IC1 through the orange path, then exits from the S1 terminal, and enters the IC2 through the R1 terminal through the second layer of wire. Then enter the GND layer and return to the negative pole of the power supply through the red path.

At high frequencies, the distribution characteristics presented by the PCB can have a large impact on the signal. The ground return we often say is a problem that is often encountered in high-frequency signals. When there is an increased current in the signal line from S1 to R1, the external magnetic field changes rapidly, which will induce a reverse current in the nearby conductors. If the ground plane of the third layer is a complete ground plane, then There will be a current on the ground plane marked by the blue dashed line, and there will also be a return flow along the blue dashed line on the TOP layer if there is a complete power plane on the TOP layer. At this time, the signal loop has the smallest current loop, the energy radiated to the outside is the smallest, and the ability to couple external signals is also the smallest. (The skin effect at high frequencies is also the smallest radiated energy, and the principle is the same.)

Since the high-frequency signal level and current change rapidly, but the change period is short, the energy required is not very large, so the chip is powered by the decoupling capacitor closest to the chip. When C1 is large enough and the response is fast enough (with very low ESR value, ceramic capacitors are usually used. The ESR of ceramic capacitors is much lower than that of tantalum capacitors.), the orange path on the top layer and the red path on the GND layer can be It is regarded as non-existent (there is a current corresponding to the power supply of the whole board, but not the current corresponding to the signal shown in the figure).

Therefore, according to the environment constructed in the figure, the entire path of the current is: from the positive electrode of C1 → the VCC of IC1 → S1 → L2 signal layer → R1 → the GND of IC2 → the via hole → the yellow path of the GND layer → the via hole → the negative electrode of the capacitor . It can be seen that there is a brown equivalent current in the vertical direction of the current, and a magnetic field will be induced in the middle. At the same time, this torus can also be easily coupled to external interference. If the signal in the figure is a clock signal, there is a group of 8bit data lines in parallel, powered by the same power supply of the same chip, and the current return path is the same. If the data lines are flipped in the same direction at the same time, a large reverse current will be induced on the clock. If the clock lines are not well matched, this crosstalk is enough to have a fatal impact on the clock signal. The intensity of this crosstalk is not proportional to the absolute value of the high and low levels of the interference source, but is proportional to the current change rate of the interference source. For a purely resistive load, the crosstalk current is proportional to dI/dt=dV /(T10%-90%*R). In the formula, dI/dt (current rate of change), dV (swing of the interference source) and R (interference source load) all refer to the parameters of the interference source (if it is a capacitive load, dI/dt is related to T10%- The square of 90% is inversely proportional.). It can be seen from the formula that low-frequency signals are not necessarily less crosstalk than high-speed signals. That is what we said: the 1KHz signal is not necessarily a low-speed signal, and the edge situation should be comprehensively considered. For a signal with a very steep edge, it contains many harmonic components and has a large amplitude at each frequency multiplication point. Therefore, you should also pay attention when selecting devices. Do not blindly choose chips with fast switching speeds, which will not only cost high, but also increase crosstalk and EMC problems.

Any adjacent power plane or other plane with suitable capacitors across the signal to provide a low reactance path to GND can act as a return plane for that signal. In ordinary applications, the corresponding chip IO power supplies for transceivers are often the same, and there are generally 0.01-0.1uF decoupling capacitors between the respective power supplies and the ground, and these capacitors are also at both ends of the signal, so the The return flow effect of the power plane is second only to the ground plane. When using other power planes for return flow, there is often no low-reactance path to ground at both ends of the signal. In this way, currents induced in adjacent planes seek the closest capacitance back to ground. If the "nearest capacitor" is far away from the start or end, the return flow has to go through a "long journey" to form a complete return path, and this path is also the return path of the adjacent signal. This same return flow The effect of channel and common ground interference is the same, which is equivalent to crosstalk between signals.

For some unavoidable cross-power splitting situations, a high-pass filter (such as a 10-ohm resistor series 680p capacitor) can be connected across a capacitor or a RC series connection at the cross-segmented place. The specific value depends on your own signal type, that is To provide a high-frequency return path, but also to isolate low-frequency crosstalk between the mutual planes). This might involve adding capacitors between the power planes, which seems a bit comical, but certainly works. If it is not allowed by some specifications, the capacitors can be led to the ground on the two planes at the split. For the case of borrowing other planes for return, it is best to add a few small capacitors to the ground at both ends of the signal to provide a return path. But this approach is often difficult to achieve. Because most of the surface space near the terminal is occupied by the matching resistor and the decoupling capacitor of the chip.

Return noise is one of the main sources of noise on the reference plane. Therefore, it is necessary to study the path and range of the return current.

3. Return path theory knowledge

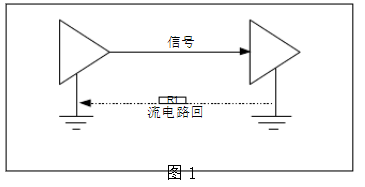

The figure below is a circuit in the printed board. There is current passing through the wires. Usually, we only see the wires used to transmit signals on the surface, from the driving end to the receiving end. In fact, the current is always in Only the loop can flow, the transmission line is what we can see, and the path of the current return is usually invisible, they usually flow back through the ground plane and the power plane, because there is no physical line, the loop path becomes difficult to estimate. They are difficult to control.

As shown in Figure 3.1, each wire and its loop on the PCB form a current loop. According to the principle of electromagnetic radiation, when a sudden current flows through the wire loop in the circuit, an electromagnetic field will be generated in the space, and it will affect other wires. Influence, this is what we usually call radiation. In order to reduce the influence of radiation, we should first understand the basic principles of radiation and parameters related to radiation intensity.

These loops act as tiny antennas at work, radiating magnetic fields into space. We simulate it with the radiation generated by the small loop antenna. Let the current be I and the small loop with area S, the measured electric field strength in the far field of free space r is:

E - electric field (V/m)

f——frequency (hz)

S——Area (m2)

I——Current (A)

r——distance (m)

——Measure the angle between the antenna and the radiating plane ()

Equation 3.1 applies to a small ring placed in free space with no reflection on the surface. In fact, our product is performed on the ground instead of free space, and reflections from nearby ground will increase the measured radiation by 6dB. Taking this into account, Equation 3.1 must be multiplied by 2. If the ground reflection is corrected and the direction of maximum radiation is assumed, then Equation 3.1 is

From Equation 3.2, the radiation is proportional to the loop current and the loop area, and proportional to the square of the current frequency.

The path of the return current in the printed circuit board is closely related to the frequency of the current. According to the basic knowledge of the circuit, the DC or low frequency current always flows in the direction of the smallest impedance; while the high frequency current always flows in the direction of the smallest inductance under the condition of a certain resistance.

If the influence of holes and grooves formed by vias on the copper-clad plane is not considered, the path with the smallest impedance, that is, the path of the low-frequency current, is composed of arc lines on the ground-clad copper plane, as shown in Figure 3.2. The density of current on each arc is related to the resistivity on that arc.

For the transmission line, the return path with the smallest inductive reactance, that is, the return path of the high frequency current, is on the copper plane directly below the signal wiring, as shown in Figure 3.3. Such a return path minimizes the space area enclosed by the entire loop, which also minimizes the magnetic field strength (or the ability to receive space radiation) radiated to the space by the loop antenna formed by this signal.

For relatively long, straight wiring, it can be regarded as an ideal transmission line. The return current of the signal propagating on it flows through the band-shaped area with the signal wiring as the central axis. The farther the distance from the central axis of the signal wiring, the smaller the current density, as shown in Figure 3.3. This relationship approximately satisfies Eq. 3.3 [4]:

Among them, I0 is the original signal current, the unit is "A, ampere"; H is the distance between the signal wiring and the copper-clad plane, the unit is "in., inches"; D is the point on the copper-clad plane The vertical distance from the signal line , in "in., inches"; I(D) is the current density at this point in "A/in., amperes per inch".

Based on Equation 3.3, Table 3.1 lists the percentage of return current flowing through a strip of width centered at the center of the transmission line as a percentage of all return currents.

Assuming inches, the current returning through the area beyond 0.035 inches from the transmission line accounts for only 13% of all return currents, and only 6.5% is divided into one side of the transmission line, and the density is very small. Therefore it can be ignored.

summary:

1. When there is a continuous, dense and complete copper-clad plane under the signal wiring, the noise interference of the signal return current to the copper-clad plane is local. Therefore, as long as the principle of localization of layout and wiring is followed, that is, the distance between digital signal lines, digital devices and analog signal lines and analog devices is artificially opened to a certain extent, the return current of digital signals to analog circuits can be greatly reduced. interference.

2. The high-frequency transient return current returns to the driver through the plane (ground or power plane) immediately adjacent to the signal trace. Termination of driver signal traces across the signal trace and the plane (ground or power plane) immediately adjacent to the signal trace.

3. The larger the surrounding area of the power and ground lines on the printed board, the greater the radiated energy they radiate. Therefore, by controlling the return path, we can minimize the surrounding area and thus control the degree of radiation.

4. Solutions to Backflow Problems

There are usually three aspects that cause reflow problems on PCB boards: chip interconnection, copper surface cutting, and via jumping. These factors are analyzed in detail below.

4.1 Reflow problems caused by chip interconnection

When a digital circuit is operating, a transition between high and low voltages occurs, which causes transient load currents to flow from the power supply into the circuit or from the circuit into the ground.

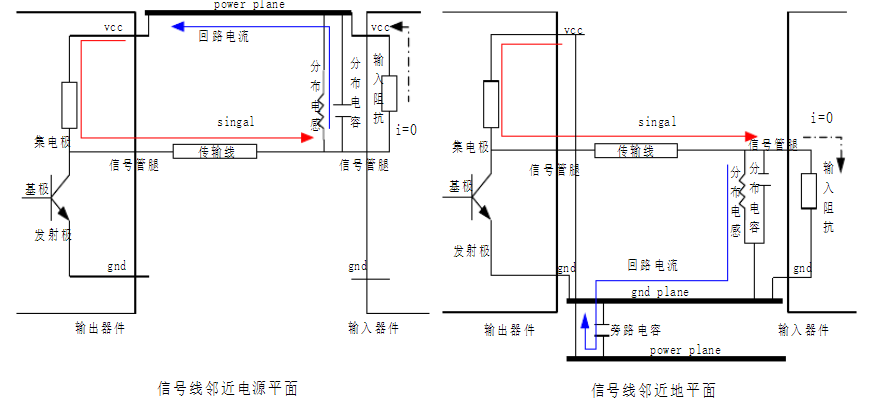

For digital devices, the input resistance of its pins can be considered as infinite, which is equivalent to an open circuit (i=0 in the figure below). In fact, the loop current is generated by the distributed capacitance and distributed inductance generated by the chip, the power supply and the ground plane. return. The following analysis will take the collector output circuit as an example of the internal circuit of the output signal.

1. The drive terminal changes from low level to high level. When the output signal jumps from a low level to a high level, it is equivalent to the output pin outputting a current to the transmission line. Since the input resistance is infinite, we think that for the chip, no current flows from the input leg. That is, then, this The current must return to the power tube leg of the output chip.

①The signal trace is close to the power plane, and the drive terminal charges the transmission line formed by the signal trace, the power plane and the terminal load. The current enters the device from the power supply pin of the driver, and flows from the output terminal of the driver to the load terminal;

The high-frequency transient return current flows back to the output of the driver on the power plane below the signal trace, and the return current directly passes through the power plane and enters the driver from the power supply pins of the driver, forming a current loop.

②The signal trace is close to the ground plane. The driver charges the transmission line formed by the signal trace, the power plane and the terminal load. The current enters the device from the power supply pin of the driver and flows from the output end of the driver to the load end;

The high-frequency transient return current flows back to the output of the driver on the ground plane under the signal trace. The return current must cross from the ground plane to the power plane and then from the driver with the help of the coupling capacitors between the power plane and the ground plane at the output of the driver. The power supply pins enter the driver, forming a current loop.

2. The drive terminal changes from high level to low level, which is equivalent to the output pin absorbing the current on the transmission line.

① Signal traces are in close proximity to the power plane.

The load discharges the transmission line formed by the signal trace, the power plane and the driver output. The current enters the device from the driver's output pin, flows out from the driver's ground pin, enters the ground plane, and passes through the power supply near the driver's ground pin. Plane and ground plane coupling capacitors, across to the power plane and back to the load;

The high-frequency transient return current flows back to the load on the power plane below the signal trace, forming a current loop.

② Signal traces are close to the ground plane.

The load discharges the transmission line formed by the signal trace, the power plane and the output terminal of the driver. The current enters the device from the output pin of the driver, flows out from the ground pin of the driver, enters the ground plane, and returns to the load terminal; high-frequency transient return current Return to the load on the ground plane below the signal trace, forming a current loop

In the vicinity of the output pins and ground pins of the driver, the coupling capacitors of the power plane and the ground plane should be arranged to provide a return path for the return current. Otherwise, the return current will find the closest coupling path between the power plane and the ground plane for return flow ( Makes the return path difficult to predict and control, resulting in crosstalk to other traces)

4.2 Solutions to the reflow problem caused by copper clad cutting

Ground and power planes reduce voltage losses due to resistors. As shown in the figure, the loop current flows back through the ground. Due to the existence of the resistance R1, a voltage drop is bound to occur at points 1 and 2. The greater the resistance, the greater the voltage drop, causing inconsistencies in the ground level. If there is a ground layer, it can be It is regarded as a signal line with infinite line width and small resistance. The loop current always flows from the ground plane closest to the signal. When there are more than one ground plane, if the signal is between two ground planes and the two are exactly the same, the loop current will pass equally on the two planes.

1. Under the condition of localization of layout and wiring, the digital ground plane and the analog ground plane share the same copper-clad plane, that is, the digital ground and the analog ground are not distinguished, and the noise of the digital circuit itself will not bring extra to the analog circuit system. noise.

2. In the digital and analog mixed circuit system, the common location of the digital ground and the analog ground is selected outside the board, that is, the two copper-clad planes are completely independent, so that the signal line between the digital circuit and the analog circuit does not have the characteristics of a transmission line, which brings the system with serious signal integrity problems. Digital circuits and analog circuits use the same power supply system, and the ground plane is not divided. In the design of digital and analog mixed circuit systems, on the basis of modular layout and localized wiring, digital circuit modules and analog circuit modules share a complete set. The undivided and undivided voltage reference plane not only does not increase the interference of digital circuits to analog circuits, but also greatly reduces the crosstalk between signals and the ground bounce noise of the system because it eliminates the "cross-channel" problem of signal lines. The accuracy of the front-end analog circuit is improved.

4.3 Solutions to Reflow Problems Caused by Vias

In the signal wiring of the printed board, if it is a multi-layer board, many signals must be connected by changing layers to complete the connection task. At this time, a large number of vias are used. There are two effects of vias on reflow: one is vias The formation of trenches blocks the reflow, and the second is the flow of reflow jumps caused by vias.

1. Trench formed by via hole

In the signal wiring of the printed board, if it is a multi-layer board, many signals must be connected by changing layers to complete the connection task. At this time, a large number of vias are used. If the vias are densely arranged in the power supply or ground plane, sometimes There will be many vias connected together, forming a so-called trench, as shown in the figure. First of all, we should analyze this situation to see if the reflow needs to go through the trench. If the return of the signal does not need to go through the trench, it will not hinder the reflow. If the loop circuit is to bypass this groove and return, the resulting antenna effect will increase sharply, causing interference to surrounding signals. Usually, after the coating data is generated, we can adjust the places where the vias are too dense to form trenches, so that there is a certain distance between the vias.

2. Layer-hopping phenomenon formed by vias

Below we take the six-layer board as an example for analysis. The six-layer board has two coating layers, the second layer is the ground layer, and the fifth layer is the power layer, so the signal return of the surface layer and the third layer is mainly in the ground layer; There are six possibilities for layer wiring: the third layer of the surface layer, the fourth layer of the surface layer, the bottom layer of the surface layer, the fourth layer of the third layer, the bottom layer of the third layer, and the bottom layer of the fourth layer. The situations can be divided into two categories: the situation where the loop current flows on the same layer and on different layers, that is, whether there is a layer jump phenomenon.

A. The case where the loop current flows on the same layer includes the third layer of the surface layer and the bottom layer of the fourth layer, as shown in the figure. In this case, the loop currents all flow on the same layer. However, according to the principle of electrostatic induction, a complete conductor in an electric field has zero internal electric field strength, and all currents flow on the surface of the conductor, the ground plane and the power supply. A plane is actually such a conductor. The vias we use are all through-holes. The holes left when these vias pass through the power and ground planes allow the flow of current on the upper and lower surfaces of the coating layer. Therefore, the return path of these signal lines is very good. , no need to take measures to improve.

B. The case where the loop current flows on different layers include the surface layer fourth layer, the surface layer bottom layer, the third layer fourth layer, and the third layer bottom layer. The bottom layer of the surface layer and the fourth layer of the third layer and the fourth layer are taken as examples to analyze the reflow situation. Signals with layer jump phenomenon need to add some bypass capacitors near the dense area of vias, usually 0.1uf magnetic chip capacitors, to provide a return path.

The above is the The basic concept of reflow, the reflow problem caused by chip interconnection we have listed for you. You can submit the following form to obtain more industry information we provide for you.

You can visit our website or contact us, and we will provide the latest consultation and solutions

Send Inquiry

Most Popular

lastest New

Send Inquiry

Send Inquiry

Mr. Zhang Peter

Tel:86-0755-29098202

Fax:86-0755-29098202

Mobile Phone:+8613544118272

Email:smt@mj880.com

Address:2nd Floor, building 34, Second Industrial Zone, Shapu Wai community, Songgang Street, Bao 'an district, Shenzhen, Guangdong

Related Products List

Mobile Site

Privacy statement: Your privacy is very important to Us. Our company promises not to disclose your personal information to any external company with out your explicit permission.

Fill in more information so that we can get in touch with you faster

Privacy statement: Your privacy is very important to Us. Our company promises not to disclose your personal information to any external company with out your explicit permission.